## 半導体製造装置とその最新技術 II

## 論理 LSI に対するテスト技術の現状と課題

九州工業大学 情報工学部 教授 梶原 誠司

SynTest Technologies,Inc. CTO 温暁青

## 1 はじめに

LSIの設計・製造技術の進歩は、チップの省面積化・高速化・低消費電力化を可能にする一方で、製造テストにおける新たな課題を生じさせている。テストの課題の解決なくして更なる技術の進歩は困難である。LSIのテスト技術開発には、大きく分けて2種類の普遍的な開発目標が存在する。一つは、テストにおいて不良を判別する能力をいかに高めるかであり、他の一つは、テストに要するコストをいかに削減するかである。

前者に関しては、テストパターンがどのような故障を検出するかが鍵となる。従来は、縮退故障モデルを前提にテストパターンを生成していたため、縮退故障の故障検出率を高めれば、テストパターンの故障検出能力は高くなるとみなされていた。スキャン設計を前提としたテストパターン生成技術は1980年代後半から飛躍的に向上し、現在では、大規模回路に対しても高い故障検出率のテストパターンの生成が可能となっている。一方で、微細化・高速化が進む中で、製造不良により生じる故障時のLSIの動作が多様化しており、接続不良(オープン故障、短絡故障)やタイミングに影響する遅延故障、クロストーク故障などが問題視されている。後者のテストコスト削減には、テスト時間の短縮、テスターコストの削減など、さまざまな要因がある。たとえば、単純にスキャン設計を用いると、フリップフロップ数の増加に比例して、テスト時間やテストデータ量が増加する。また、通常動作速

度でテストすることにも障害が生じるため、タイミングに影響するような故障を捕らえにくくなる。

本稿では、テストの品質向上の取り組みにおいて考慮すべき縮退故障に代わる故障モデル、および、その検出法について、現状と課題を紹介する。次に、テスト容易化技術の現状とそれに関連したテストコスト削減に向けた取り組みを紹介する。

### 2 故障モデルと対策

#### 2.1 単一縮退故障モデルの限界

単一縮退故障モデルは、回路内のどこか一箇所の信号線が、 論理値0または1に固定すると仮定した故障モデルである。 実際に生じる欠陥が論理故障(欠陥が論理値の異常を示す故 障)として現れる場合には、その故障を検出するテストパターンが縮退故障を検出テストパターンとなる。つまり、基本的 に単一縮退故障を検出するテストパターンは、他の故障を検 出するための必要条件を満たすテストパターンである。しか しながら、故障動作の多様化により、単に縮退故障を検出す ることを満足するテストパターンだけでは、現実に生じる故 障の検出に不十分となっている。

#### 2.2 静的動作における故障

論理回路の静的動作に影響を及ぼす物理欠陥をゲートレベルで捕える故障モデルとしては、単一縮退故障の他、多重縮退故障、オープン故障、およびブリッジ故障があり、それぞれ複数箇所に発生する欠陥、信号線の断線、および信号線間の短絡に対応している。これらの故障モデルは物理欠陥をよりよく表しているが、故障シミュレーションやテスト生成の処理が複雑化する。特に、欠陥電圧が中間値の場合、故障の論理値が定まらないというByzantine 現象が起きるため、問題は更に深刻になる。最近、複雑な故障モデルを使わず、一つの縮退故障を異なるテストパターンにより複数回検出するN-検出テスト生成が用いられるようになり、その複雑な故障の検出への有効性も実証されている。

また、静止状態でのリーク電流(IDDQ)で故障の有無を調べる場合は、トランジスタ短絡故障がよく用いられる。これは、CMOSトランジスタの4つの端子間に短絡を仮定する故障モデルである。故障影響の伝搬が不要なので、論理故障よ

# 第14回 テスト

り検出しやすいが、LSIの微細化・低電圧化が進むにつれ、 その有効性が薄れつつある。

#### 2.3 動的動作における故障

クロック信号を含む信号値の変化により誤動作が顕在化するような故障の代表例は、遅延故障である。遅延故障にも、トランジション故障やゲート遅延故障のように、生じる原因が局所的な欠陥によるものや、パス遅延故障のように信号伝搬経路上の遅延が蓄積して誤動作を生じさせるものなど様々である。一般に遅延故障の検出には、信号値変化がフリップフロップや外部出力に伝搬するように、連続する2つのテストパターンを印加すればよい(2パターンテストとも呼ばれる)。

遅延故障そのものは20年近く前から確立されていた故障モデルである。しかしながら、製造プロセスの微細化は、性能予測、性能テストにおける不確定要素を増加させ、遅延故障を含む動的動作における故障の検出を複雑化している。これらの故障には、発生原因が必ずしも欠陥によるものではなく、設計や特定のテストパターンに起因して生じるものも多い。配線間のクロストークによるグリッチの発生や遅延の増加・減少、IRドロップのような電源ノイズによる遅延の増加は、その一例である。プロセスばらつきが原因の回路性能低下や、発熱にともなう遅延の増加も、故障といえるのかは微妙である。また、故障検査に使うテストパターンは、通常動作時と比較して、回路内の信号値変化を2倍から3倍増加させることが知られており、故障のない回路であっても、テストパターンが誤動作の原因となることもある。

動的動作における故障検出の重要性は高まっているが、必ずしもそれに十分対処できる技術が確立しているとは言えない。実用化を目指した今後の研究が待たれるところである。

## 3 テスト容易化技術

#### 3.1 スキャン設計

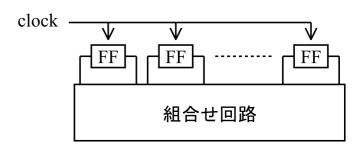

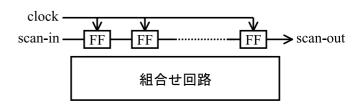

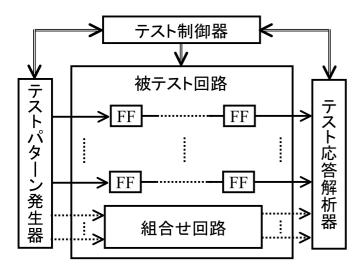

一般の論理回路は、通常動作に必要な機能だけ持つように設計したのではテストを効率的に実施できないため、テスト時のみに利用する機能を持たせて設計される。この考え方は、テスト容易化設計(Design for Testability)と呼ばれている。その代表的な手法として、スキャン設計がよく知られている。フリップフロップにシフトレジスタ機能を持たせることで、内部信号値の可観測性や可制御性が向上する(図1、図2)。その結果、テスト生成時には回路を組合せ回路として扱うことができ、縮退故障に対して高い故障検出率のテストパターンを容易に生成できるようになる。

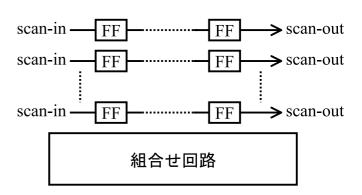

一方でスキャン設計には、フリップフロップ数が増加するとテスト時間が増大するという欠点もある。その欠点を緩和する手法として、図3のように複数本のスキャンチェーンを

図1 順序回路モデル

図2 スキャン動作時の回路

図3 多重スキャン回路(クロックは省略)

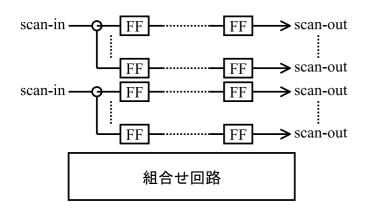

並列に動作させる多重スキャン設計 (Multiple scan design) が用いられている。単純には、スキャンチェーンを n 本にすれば、テスト時間は n 分の 1 にできる。しかし、テスト時間は短くなっても、テストデータ量は変わらない。多重スキャン設計におけるテストデータ量を削減する方法として、図 4 のように一本のスキャン入力により複数のスキャンチェーンを制御する方法も提案されている。m 本のスキャンチェーンを束ねることで、うまくいけばテストデータ量は m 分の 1 になる。一方で、フリップフロップ間に信号値の相関が生じるため、故障検出率が低下しないように、直列に一本のスキャンチェーンを構成するようなモードも用意し、スキャンチェーンの構成を動的に変更する必要がある。

### 3.2 BIST への期待と障壁

論理 BIST (Built-In Self-Test) は、テストパターン発生、テスト応答解析、およびテスト制御などの機能を被テスト回路と同じチップ内に実現するテスト方式である。図5にその

## 半導体製造装置とその最新技術Ⅱ

図4 一入力の多重スキャン(クロックは省略)

図5 論理 BIST の概略

概略を示す。BIST の利点としては、廉価なテスタの使用によるテストのコストの削減や、実速度テスト(At-Speed Test)によるテスト品質の向上の他、最小限の外部アクセスで十分なことから SoC (System-on-a-Chip) のテストに適しているなどがあげられる。

論理 BIST の実現には、BIST 回路の設計が肝心である。テストパターン発生とテスト応答解析をできるだけ少ないオーバーヘッドで効果的に行い、テストクロック信号やテスト制御信号を正しく生成することは勿論、その物理設計も容易にできなければならない。

【テストパターン発生器】LFSR(Linear Feedback Shift Register)による擬似乱数発生器がよく用いられるが、遅延故障は勿論、単一縮退故障でも十分な故障検出率を得るのは難しい。このため、リシーディング(Reseeding)、重み付き、ビット転換(Bit-Flipping)などで被テスト回路への入力を改善したり、被テスト回路が乱数パターンでテストしやすくなるようテストポイントを挿入したりする対策が重要となる

が、外部テストデータ量やオーバーヘッドの増加、回路遅延 への影響などにも注意する必要がある。

【テスト応答解析器】MISR(Multiple Input Signature Register)によるテスト応答圧縮がよく使われる。テスト応答は MISR に重ねて入力され、最後にそのシグネチャが得られるが、シグネチャの一義性を保つため、不確定値が MISR に入ってはならない。このため、メモリやアナログ部分などの不確定値の発生源をブロックする必要がある。また、これによる回路遅延の増加を最小限に抑えなければならない。

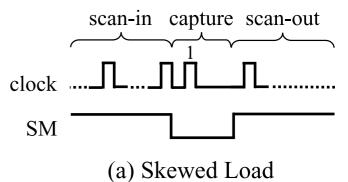

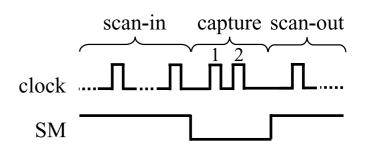

【テスト制御器】この設計においては、複数クロックドメーン間のスキューを考慮に入れたテストクロック信号と、シフトからキャプチャへの切り替えを制御するスキャン・モード (SM) 信号が実速度テストにとって重要である。実速度での切り替え (Skewed Load:図6(a)) の場合は、故障検出率が高いが、SMをクロックとして扱う必要があり物理設計が困難になる。一方、シフトから一つ目のキャプチャまで十分な遅延をとり、一つ目のキャプチャから二つ目のキャプチャへ実速度で移行する方式 (Broadside Load:図6(b)) の場合は、低速かつ低精度の SM 信号でも十分であるため物理設計が簡単になるが、故障検出率が低くなり、故障シミュレーションも複雑になる。

## (b) Broadside Load

図6 実速度テストの方式

# 第14回 テスト

#### 3.3 テスト圧縮技術

テスタのメモリにテストパターンと期待値を格納し、テスタでテストパターンの印加とテスト応答の解析を行うテスト方式は、被テスト回路への影響が少ないため、LSIテストで広く用いられている。しかし、LSIの大規模化・複雑化が進むにつれ、テストデータ量は急激に増大してきている。リロード、メモリ増設、テスタの更新などの対処法があるが、いずれもテストコストの急増につながっている。このため、テストデータ量をテストパターン圧縮とテスト応答圧縮によって削減するテスト圧縮技術が注目されている。

テストパターン圧縮にはテストコンパックション(Test Compaction)とテストコンプレッション(Test Compression)の二通りのアプローチがある。前者では、テスト生成において高い故障検出率を少ないテストベクトルで実現することを目標とする。そのために、テストベクトルのマージや冗長なテストベクトルの除去などが行なわれる。後者では、テストパターンの表現方法を変換して格納するテストデータ量を削減し、また、テスト時にはチップに埋め込まれた付加回路によりテストデータを元のテストパターンに展開してから、被テスト回路に印加する。その変換には、リシーディングを用いるLFSRや符号化手法などがよく使われる。

テスト応答圧縮には、MISRによるシグネチャの生成が一番有効であるが、不確定値をブロックする必要があるため、被テスト回路への影響が大きい。このため、不確定値の存在を許容する XOR 回路による空間圧縮がよく用いられる。この場合、不確定値やエイリアシング(Aliasing)によって故障検出率が低下する可能性があるので、XOR 圧縮器による制約を考慮したテスト生成やマスク回路の使用で対処する必要がある。

## 4 まとめ

LSIのテスト技術は、設計・製造技術の進歩とともに常に新たな課題を抱え、それを解決すべく技術が発展してきた。その中には、論理 BIST のように、20年以上も前に考案されながら実用的にはあまり見向きされなかった技術が最近になって脚光を浴びているケースもある。今後も進む LSI の微細化やシステム化の流れの中で、テスト技術が抵抗勢力とならないよう、新たな技術の開発や旧来技術の改善に知恵を絞っていくことが望まれている。

(かじはら せいじ・おん ぎょうせい)